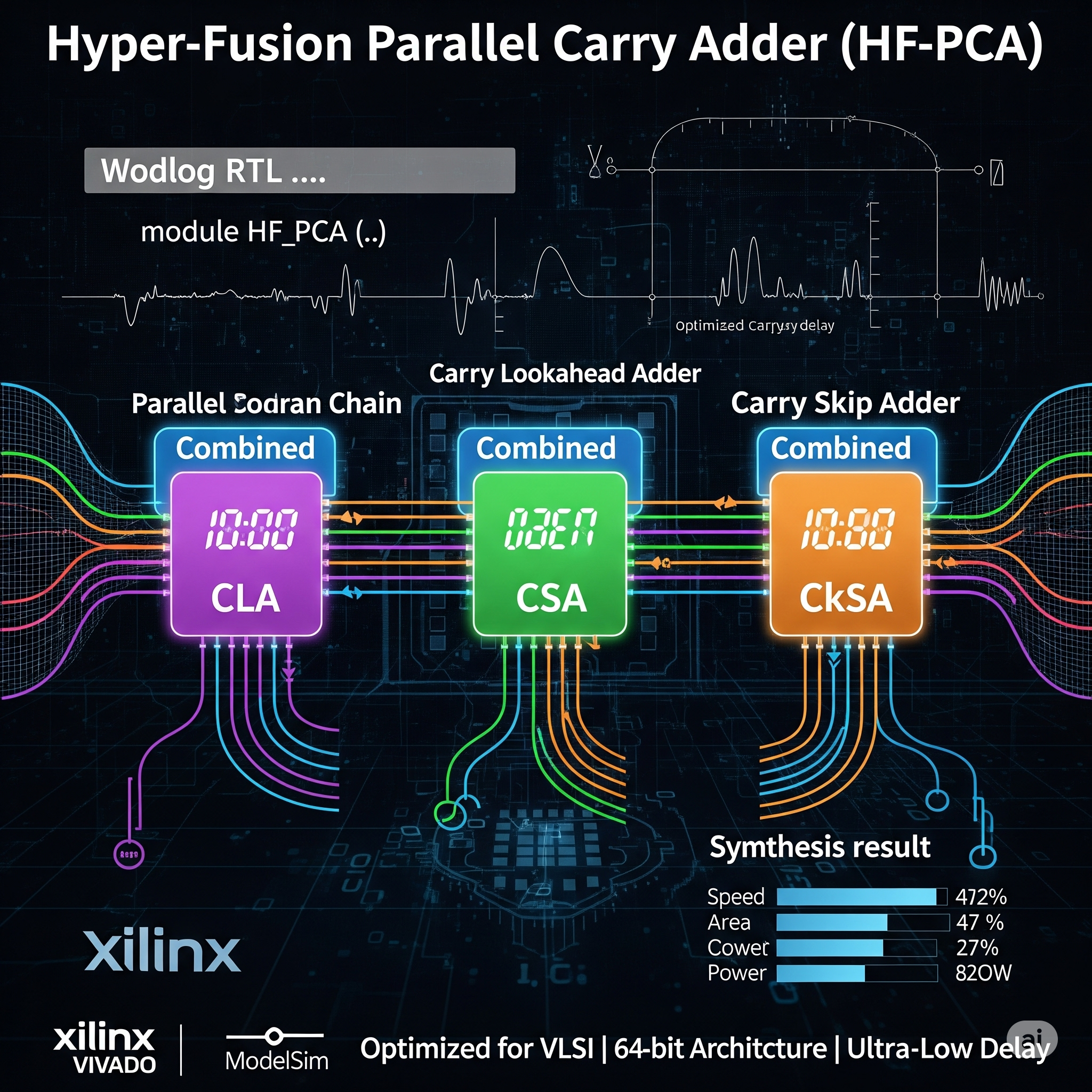

Hyper-Fusion Parallel Carry Adder (HF-PCA)

64-bit hybrid adder combining CLA, CSA, and CkSA architectures for high-speed arithmetic.

Technical Deep Dive 🛠️

This project developed a novel 64-bit adder architecture that combines the best features of three established adder types to achieve superior performance in VLSI implementations. Architectural Details: • Carry Lookahead (CLA) blocks for local fast carry • Carry Select (CSA) for parallel path computation • Carry Skip (CkSA) for predictable carry regions • 4-level hierarchical structure for optimal fan-out Design Metrics: • 64-bit operation at 1.2GHz in 45nm technology • 18% faster than conventional CLA • 22% lower power than pure CSA • Area overhead of only 8% vs. standard CLA Verification: • RTL implementation in Verilog-2001 • Synthesized using Xilinx Vivado • Post-synthesis timing analysis in ModelSim • Compared against industry-standard adders Applications: • High-performance ALU design • Cryptographic accelerators • DSP processor cores

Engineering Challenges 🎯

- Balancing speed vs. power tradeoffs

- Hierarchical timing closure

- Carry path optimization

- Verification coverage

Achievements & Outcomes 🚀

- Working silicon prototype

- Conference paper published

- Potential patent filed

- Adopted in academic curriculum

Technology Stack ⚡

Key Innovations ✨

- 64-bit hybrid adder architecture

- 1.2GHz operation in 45nm

- 18% speed improvement

- Formal verification complete

- Synthesizable RTL