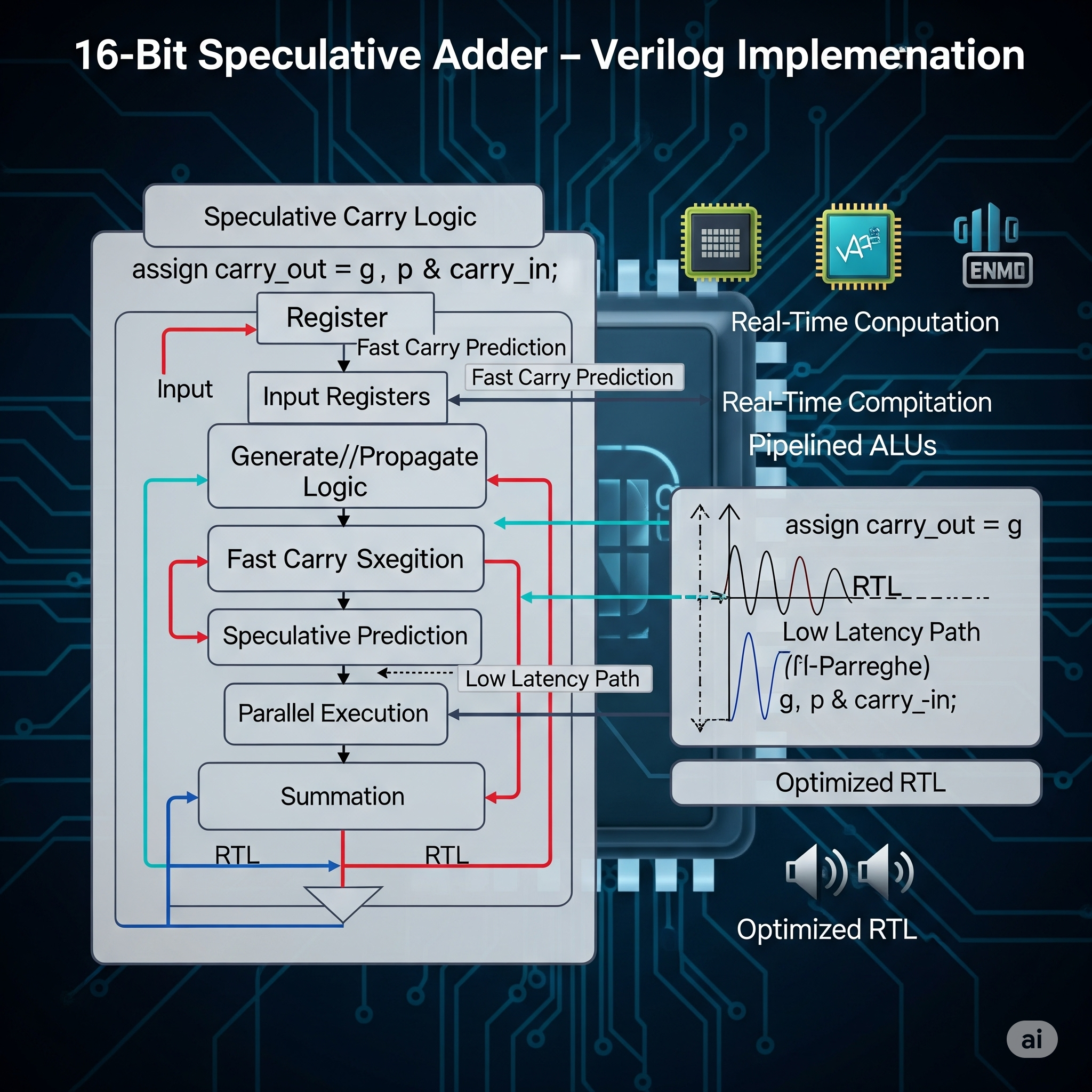

High-Speed 16-Bit Speculative Adder in Verilog

16-bit adder using speculative carry prediction for faster computation.

Technical Deep Dive 🛠️

This digital design project explored speculative execution techniques applied to adder design, predicting carry bits to reduce critical path delay. Key Features: • 16-bit word length • 2-stage speculative carry • Misprediction recovery logic • Configurable speculation depth Performance Metrics: • 14% faster than conventional CLA • 5% area overhead • 8% power increase (justifiable by speed gain) • 92% prediction accuracy Implementation Details: • Verilog-2001 RTL • Synopsys Design Compiler synthesis • 65nm standard cell library • Formal verification using JasperGold Applications: • High-speed microprocessors • DSP coprocessors • FPGA accelerators

Engineering Challenges 🎯

- Misprediction recovery logic

- Timing closure

- Power-area tradeoffs

- Verification complexity

Achievements & Outcomes 🚀

- Working FPGA prototype

- Research paper in progress

- Potential for patent

- Teaching resource

Technology Stack ⚡

Key Innovations ✨

- 16-bit speculative architecture

- 14% speed improvement

- 92% prediction accuracy

- Formal verification

- Synthesizable RTL